先建立直觉,再进入工程细节

这一页不只给定义,而是按小白能跟上的顺序拆开:先用类比建立画面,再看真实工程怎么用,最后通过实验、误区和检查问题把知识固定下来。

入门解释

时序逻辑不只是看现在输入,还会记住之前发生了什么,所以它更像有记忆的系统。

标准解释

时序逻辑由组合逻辑加存储单元构成,输出受当前输入与历史状态共同影响。

进阶解释

建立时间、保持时间、时钟偏斜和亚稳态是时序系统设计的关键风险点。

生活类比

时序逻辑像有记忆的机器:它不仅看当前输入,还看自己之前处在什么状态。红绿灯控制、电梯控制、通信协议握手,都必须记住过去发生了什么。

工程中怎么看

工程里设计时序逻辑,核心是状态、时钟、复位和状态转移。你要知道什么时候采样输入、什么时候更新状态、复位后从哪里开始,以及输出是由当前状态还是下一状态决定。

它在系统里负责什么

时序逻辑让数字系统从一次性计算变成连续运行的系统。CPU 取指执行、总线传输、外设通信、缓存控制和流水线推进,都依赖稳定的时序逻辑。

关键知识点

- · 状态

- · 时钟

- · 建立保持时间

- · 状态机

典型应用

- · 计数器

- · 状态机

- · 流水线

- · 通信协议控制

做一个三状态 LED 控制器

定义三个状态:等待、闪烁、常亮,并画出状态转移图。

用按键作为输入,规定每按一次切换到下一个状态。

加入上电复位,让系统一定从等待状态开始。

用仿真或开发板观察状态变化,记录每个状态下输出行为。

加入按键消抖,体会真实输入并不总是干净的数字边沿。

常见误区

没有设计清晰复位状态,上电后系统进入未知状态。

把异步输入直接送入时序电路,造成亚稳态风险。

状态机没有覆盖异常状态,跑飞后无法自恢复。

忽略建立时间和保持时间,导致高频下偶发错误。

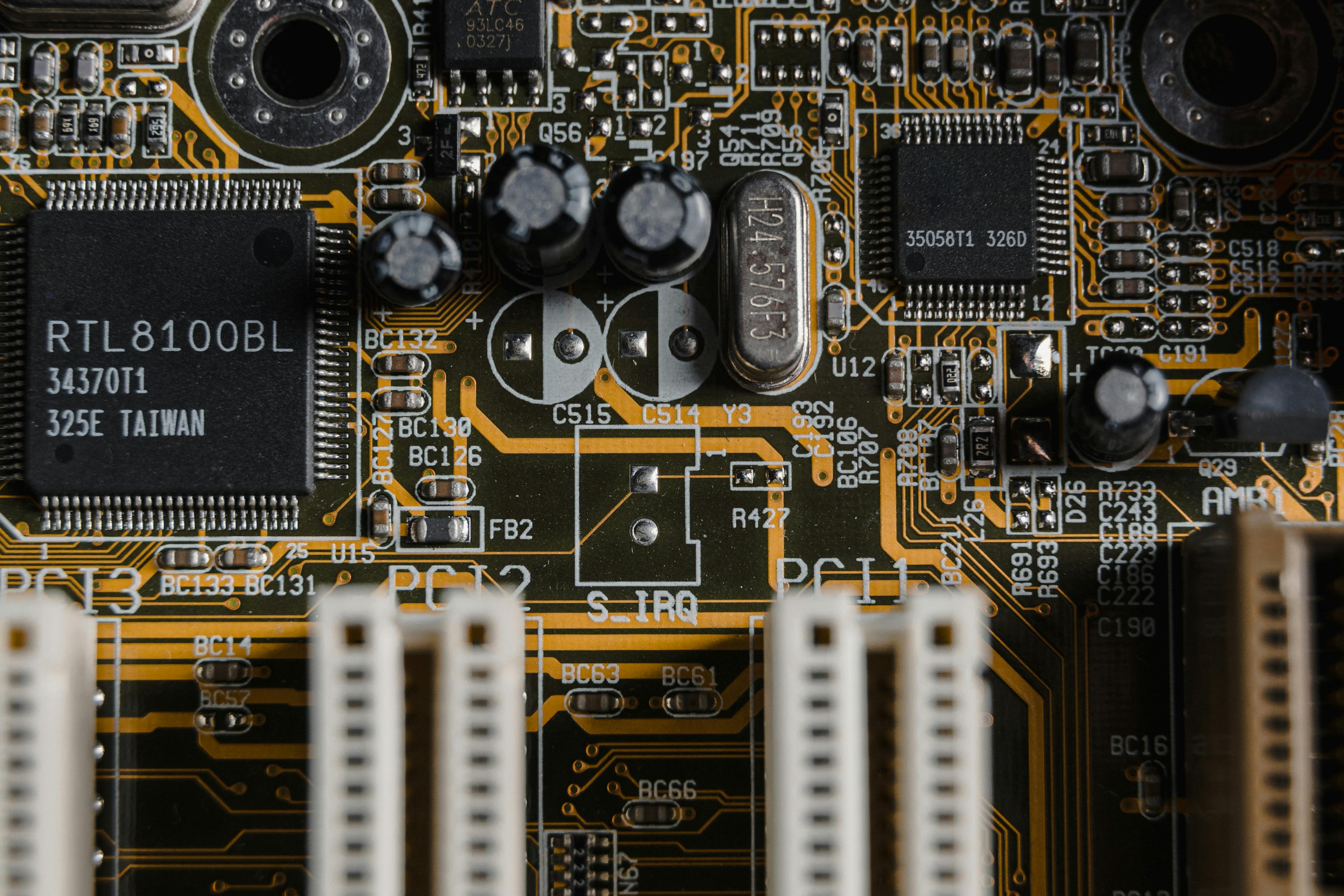

Typical Circuit

状态机:组合逻辑加触发器

让电路记住当前状态并按时钟转移

时序逻辑比组合逻辑多了状态寄存器。组合逻辑根据当前状态和输入算出下一状态,时钟边沿到来时触发器把下一状态锁存为当前状态。

波形怎么看:输入可以在周期内变化,但状态只在有效时钟边沿更新。输出可以由当前状态决定,也可以由状态和输入共同决定。

参考画法:同步有限状态机 FSM 结构。页面中的 SVG 为本站重新绘制,用于教学说明。

典型应用电路

SCHEMATIC关键波形 / 时序

WAVEFORM读完要能回答

CHECK 01

为什么时序逻辑必须关心时钟?

CHECK 02

状态机的状态、输入、输出和转移条件分别是什么?

CHECK 03

复位信号为什么重要?

CHECK 04

异步按键为什么不能直接当作稳定时钟域信号?

术语拆解

状态

系统当前记住的内部信息,决定下一步行为。

时钟

让寄存器同步更新的节拍信号。

建立时间

数据在时钟边沿前必须稳定的最短时间。

亚稳态

触发器在不满足时序要求时可能短暂无法确定输出。

和下一个节点的关系

时序逻辑的基本存储单元是触发器。理解触发器后,你会知道一个 bit 是怎样被硬件真正记住的。