先建立直觉,再进入工程细节

这一页不只给定义,而是按小白能跟上的顺序拆开:先用类比建立画面,再看真实工程怎么用,最后通过实验、误区和检查问题把知识固定下来。

入门解释

组合逻辑像一台即时计算器,只看你现在按了什么键,不记住上一次按了什么。

标准解释

编码器、译码器、加法器和多路选择器都属于组合逻辑,常用卡诺图做化简。

进阶解释

复杂组合逻辑需要平衡面积、延迟与功耗,关键路径优化直接影响后级时钟频率上限。

生活类比

组合逻辑像一台没有记忆的即时计算器:输入是什么,输出就按规则立刻算出来。它不会记得上一次输入,所以同样输入永远得到同样输出。

工程中怎么看

工程上设计组合逻辑,要把需求拆成输入、输出、真值表、表达式和门级实现。规模稍大时,还要考虑关键路径延迟,因为最慢那条逻辑路径会限制后级时钟频率。

它在系统里负责什么

组合逻辑承担计算、选择、译码和条件判断。ALU、地址译码、外设片选、中断优先级编码等模块,都大量依赖组合逻辑。

关键知识点

- · 当前输入决定输出

- · 加法器

- · 译码器

- · 关键路径

典型应用

- · 地址译码

- · ALU 子模块

- · 数据选择

- · 控制逻辑

设计一个 2 位比较器

定义两个 2 位输入 A、B,以及 A>B、A=B、A<B 三个输出。

列出所有输入组合,写出对应输出。

从真值表推导表达式,或用卡诺图做简单化简。

用仿真工具验证所有输入组合是否正确。

观察哪条输入到输出路径经过的门最多,理解关键路径概念。

常见误区

需求没写清楚就开始画门电路,导致输入输出定义混乱。

只追求门数量少,忽略传播延迟和毛刺。

把需要记忆状态的问题误写成组合逻辑,结果输出无法稳定表达历史。

忘记默认分支,让硬件描述语言综合出锁存器。

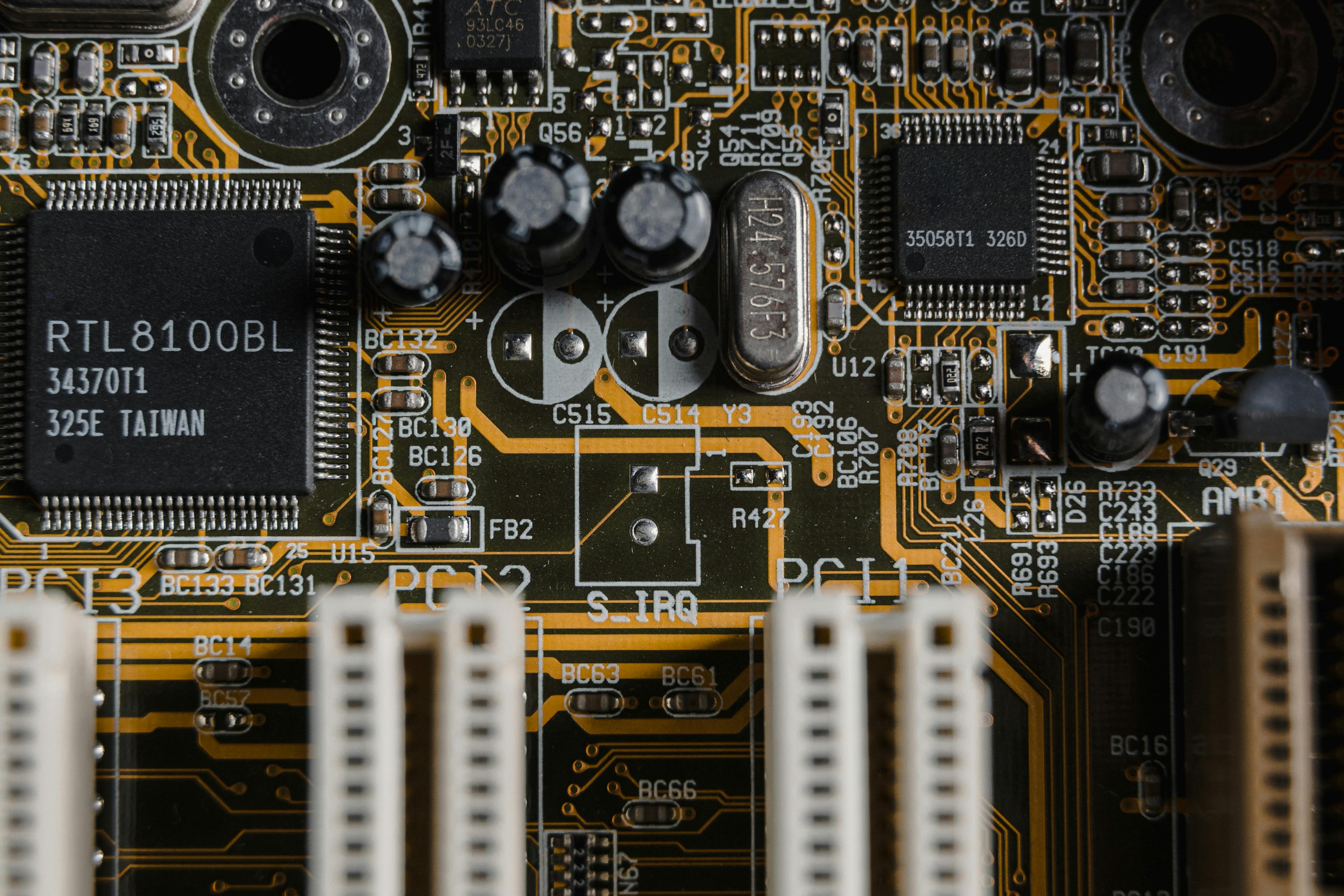

Typical Circuit

半加器:XOR 生成和,AND 生成进位

把两个 1 bit 输入相加

组合逻辑没有记忆,只看当前输入。半加器用 XOR 得到 Sum,用 AND 得到 Carry;多个半加器/全加器级联后,就能组成多位加法器和 ALU 的一部分。

波形怎么看:A、B 同为 1 时 Carry 为 1;只有一个输入为 1 时 Sum 为 1。输出跟随输入变化,但会受门延迟影响。

参考画法:半加器真值表与门级实现。页面中的 SVG 为本站重新绘制,用于教学说明。

典型应用电路

SCHEMATIC关键波形 / 时序

WAVEFORM读完要能回答

CHECK 01

组合逻辑和时序逻辑的根本区别是什么?

CHECK 02

什么是关键路径,为什么它会限制速度?

CHECK 03

为什么译码器、选择器属于组合逻辑?

CHECK 04

HDL 中遗漏默认赋值为什么可能综合出锁存器?

术语拆解

译码器

把编码输入转换成某一路输出有效的组合逻辑。

选择器

根据选择信号从多路输入中选一路输出。

关键路径

从输入到输出延迟最长的逻辑路径。

卡诺图

用于化简小规模布尔表达式的图形方法。

和下一个节点的关系

当电路需要记住过去,就必须加入触发器、寄存器和时钟。时序逻辑会让系统拥有状态,复杂控制才真正开始。