先建立直觉,再进入工程细节

这一页不只给定义,而是按小白能跟上的顺序拆开:先用类比建立画面,再看真实工程怎么用,最后通过实验、误区和检查问题把知识固定下来。

入门解释

逻辑门就是电子世界里的条件判断。两个输入都为 1,输出才为 1,这就是与门。

标准解释

与、或、非、异或等门电路构成数字系统基础,可通过真值表描述输入输出关系。

进阶解释

门延迟、扇入扇出、竞争冒险和噪声容限决定逻辑门在真实系统中的稳定性与时序边界。

生活类比

逻辑门就是电路里的判断规则。与门要求条件同时满足,或门只要满足一个条件,非门负责取反;这些规则看起来像数学,其实底层仍然是晶体管的导通与截止。

工程中怎么看

工程里使用逻辑门,除了真值表,还要考虑电平标准、传播延迟、扇出能力和噪声容限。理想逻辑里 1 会立刻变成输出,真实芯片里信号需要时间传播,边沿还可能被噪声影响。

它在系统里负责什么

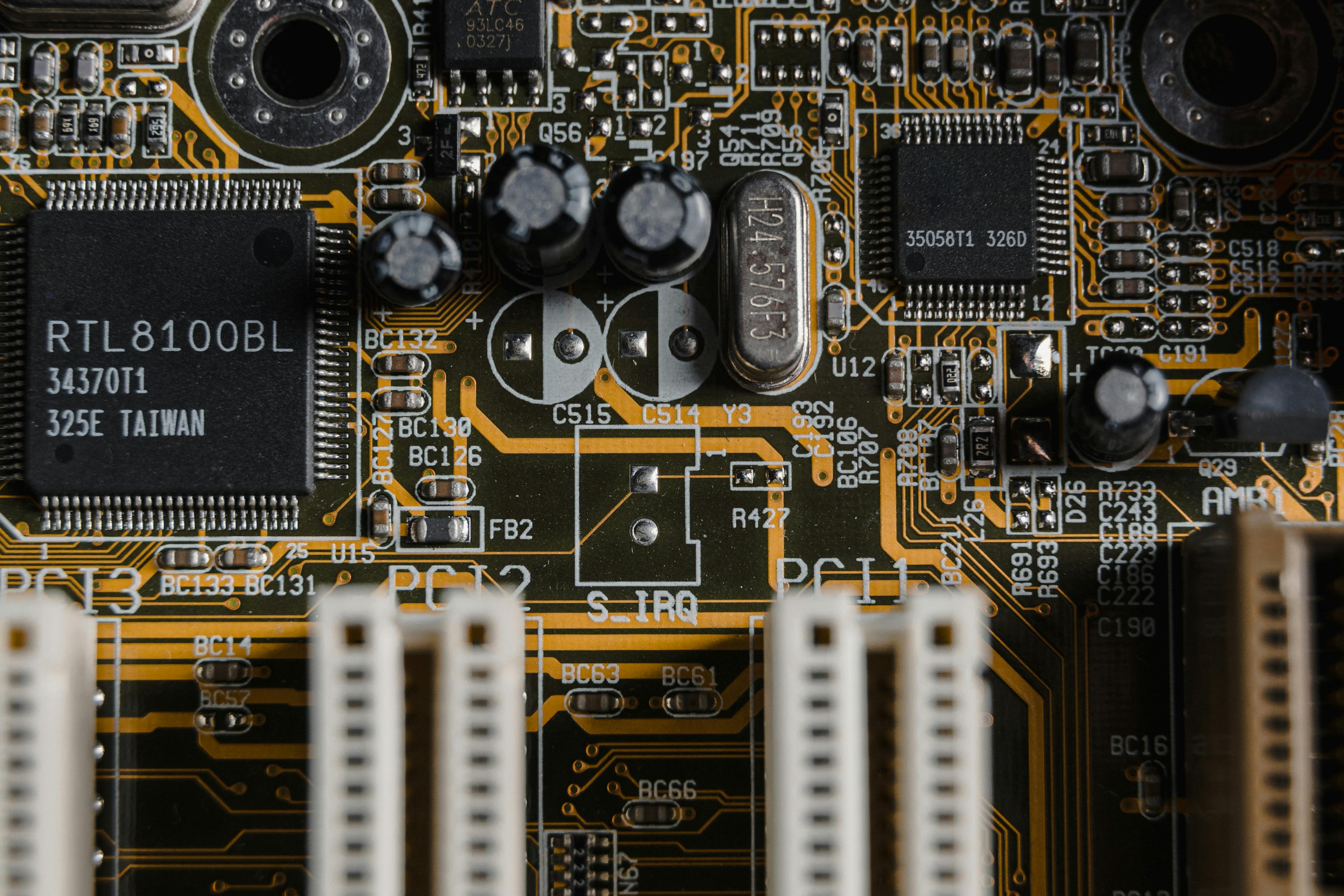

逻辑门把器件行为抽象成布尔运算,是数字电路的最小语言。CPU、MCU、内存控制器、总线协议和外设控制,最终都可以回到大量逻辑门的组合与时序。

关键知识点

- · 真值表

- · 布尔代数

- · 与或非

- · 门延迟

典型应用

- · 译码器

- · 加法器

- · 状态机

- · 接口控制

从真值表搭出一个小判断电路

列出一个需求:例如两个按键都按下时 LED 亮,写出输入 A、B 和输出 Y 的真值表。

用 74HC08 与门芯片或仿真工具搭建电路,观察输出是否符合真值表。

把需求改成任意一个按键按下就亮,替换为或门并更新真值表。

加入非门,让某个条件变成“没有按下时成立”。

用示波器或逻辑分析仪观察输入变化到输出变化之间的延迟。

常见误区

只背与或非符号,不会写真值表,导致复杂逻辑无法拆解。

忽略 3.3V 与 5V 电平兼容问题,直接把两个模块相连。

认为逻辑输出瞬间变化,忽略传播延迟和毛刺。

多个输出直接短接在一起,造成芯片互相拉扯甚至烧毁。

Typical Circuit

CMOS 反相器与逻辑电平

从一个输入生成相反的数字输出

最基础的 CMOS 逻辑门由上拉 PMOS 和下拉 NMOS 组成。输入为 0 时 PMOS 导通、输出被拉到 VDD;输入为 1 时 NMOS 导通、输出被拉到 GND。

波形怎么看:输入波形翻转后,输出会以相反方向变化;真实芯片会有传播延迟,所以输出边沿会晚一点出现。

参考画法:CMOS inverter 标准门电路。页面中的 SVG 为本站重新绘制,用于教学说明。

典型应用电路

SCHEMATIC关键波形 / 时序

WAVEFORM读完要能回答

CHECK 01

真值表为什么是理解逻辑门最可靠的方法?

CHECK 02

高电平和低电平一定等于电源电压和 0V 吗?

CHECK 03

传播延迟会在什么场景下造成问题?

CHECK 04

为什么不能把两个普通逻辑输出直接并联?

术语拆解

真值表

列出所有输入组合和对应输出的表,是逻辑设计的基础。

传播延迟

输入变化到输出稳定之间的时间差。

噪声容限

电平被干扰后仍能被识别为正确 0 或 1 的余量。

扇出

一个逻辑输出可以可靠驱动多少个输入。

和下一个节点的关系

单个逻辑门只能表达很小的判断。把许多门组合起来,就能做译码器、选择器、加法器等组合逻辑模块。